# TOSHIBA

# **TOSHIBA CORPORATION**

Semiconductor Company

# **Document Change Notification**

The purpose of this notification is to inform customers about the launch of the Pb free version of the device. The introduction of a Pb-free replacement affects the datasheet. Please understand that this notification is intended as a temporary substitute for a revision of the datasheet.

Changes to the datasheet may include the following, though not all of them may apply to this particular device.

- 1. Part number

- Example: TMPxxxxxF TMPxxxxxFG

All references to the previous part number were left unchanged in body text. The new part number is indicated on the prelims pages (cover page and this notification).

2. Package code and package dimensions

Example: LQFP100-P-1414-0.50C LQFP100-P-1414-0.50F

All references to the previous package code and package dimensions were left unchanged in body text. The new ones are indicated on the prelims pages.

3. Addition of notes on lead solderability

Now that the device is Pb-free, notes on lead solderability have been added.

4. RESTRICTIONS ON PRODUCT USE

The previous (obsolete) provision might be left unchanged on page 1 of body text. A new replacement is included on the next page.

5. Publication date of the datasheet

The publication date at the lower right corner of the prelims pages applies to the new device.

#### 1. Part number

#### 2. Package code and dimensions

| Previous Part Number<br>(in Body Text) | Previous Package Code<br>(in Body Text) | New Part Number | New Package Code   | OTP          |

|----------------------------------------|-----------------------------------------|-----------------|--------------------|--------------|

| TMP47C241N                             | P-SDIP28-400-1.78                       | TMP47C241NG     | SDIP28-P-400-1.78  | TMP47P241VNG |

| TMP47C241M                             | P-SOP28-450-1.27                        | TMP47C241MG     | SOP28-P-450-1.27B) | TMP47P241VMG |

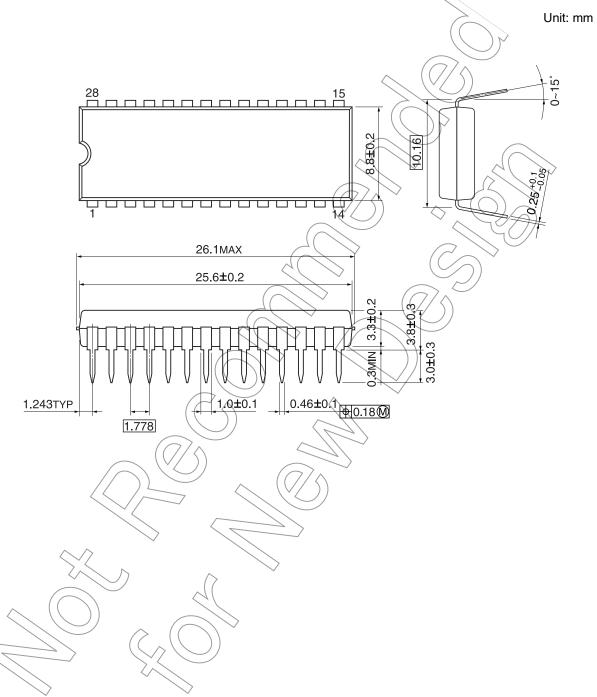

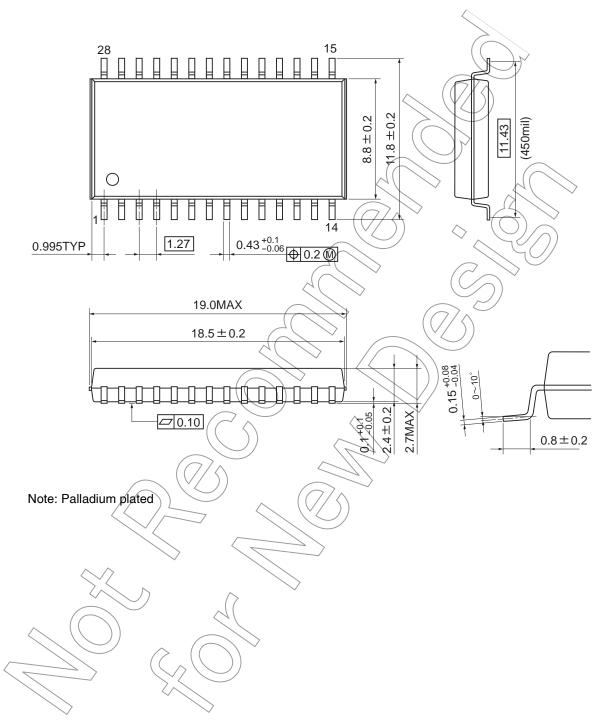

\*: For the dimensions of the new package, see the attached Package Dimensions diagram.

#### 3. Addition of notes on lead solderability

The following solderability test is conducted on the new device.

#### Lead solderability of Pb-free devices (with the G suffix)

| Test          | Test Conditions                                                                                                                                                                                                                                                                                                                                                   | Remark                                                                   |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| Solderability | <ul> <li>(1) Use of Lead (Pb)</li> <li>solder bath temperature = 230°C</li> <li>dipping time = 5 seconds</li> <li>the number of times = once</li> <li>use of R-type flux</li> <li>(2) Use of Lead (Pb)-Free</li> <li>solder bath temperature = 245°C</li> <li>dipping time = 5 seconds</li> <li>the number of times = once</li> <li>use of R-type flux</li> </ul> | Leads with over 95% solder coverage<br>till lead forming are acceptable. |

# 4. RESTRICTIONS ON PRODUCT USE

The following replaces the "RESTRICTIONS ON PRODUCT USE" on page 1 of body text.

#### **RESTRICTIONS ON PRODUCT USE**

• The information contained herein is subject to change without notice.

20070701-EN

• TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc.

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in his document shall be made at the clustomer's own risk.

- The products described in this document shall not be used or embedded to any downstream products of which manufacture, use and/or sale are prohibited under any applicable laws and regulations.

- The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patents or other rights of TOSHIBA or the third parties.

- Please contact your sales representative for product-by-product details in this document regarding RoHS compatibility. Please use these products in this document in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances. Toshiba assumes no liability for damage or losses occurring as a result of noncompliance with applicable laws and regulations.

- For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Quality and Reliability Assurance/Handling Precautions.

# 5. Publication date of the datasheet

The publication date of this datasheet is printed at the lower right corner of this notification.

(Annex)

Package Dimensions

SDIP28-P-400-1.78

SOP28-P-450-1.27B

Unit: mm

CMOS 4-Bit Microcontroller

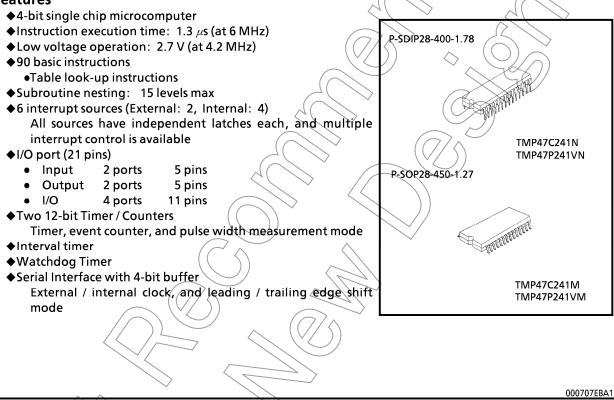

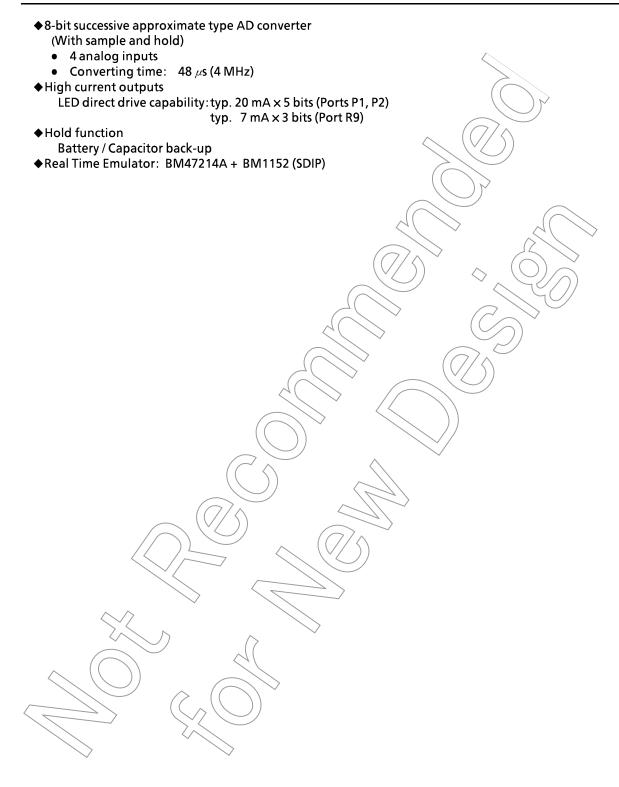

# TMP47C241N TMP47C241M

The TMP47C241 are high speed and high performance 4-bit single chip micro computers, integrating 8-bit AD converter, watchdog timer and serial Interface based on the TLCS-47 series.

| Part No.   | ROM          | RAM         | Rackage                       |

|------------|--------------|-------------|-------------------------------|

| TMP47C241N | 2019 v 9 hit | 128 x 4-bit | P-SDIP28-400-1.78 TMP47P241VN |

| TMP47C241M | 2048 x 8-bit | 126 X 4-DIL | P-SOP28-450-1.27 TMP47P241VM  |

| -          |              |             |                               |

#### Features

For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Quality and Reliability Assurance / Handling Precautions.

TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodity injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products precises," or "TOSHIBA products Reliability Handbook" etc.

The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are used in struments, attraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, medical instruments, traffic signal instruments, combustion control instruments, medical instruments, traffic signal instruments, combustion control instruments, medical instruments, the used with a subject to the foreign exchange and foreign trade laws.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third property or other rights of TOSHIBA CORPORATION or others.

# TOSHIBA

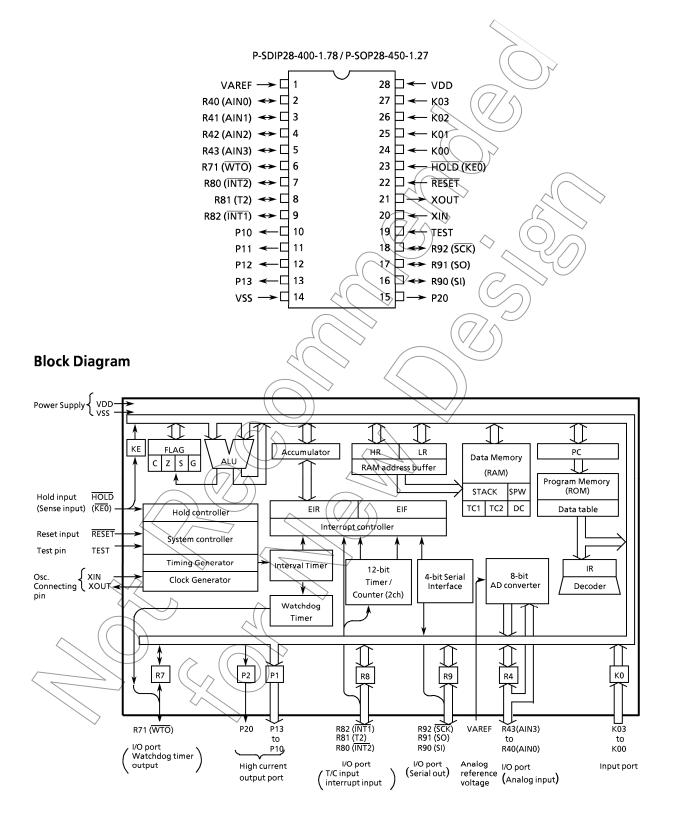

#### Pin Assignment (Top View)

# **Pin Function**

| Pin Name                       | Input / Output | Functions                                                                                                         |                                  |  |  |  |  |  |

|--------------------------------|----------------|-------------------------------------------------------------------------------------------------------------------|----------------------------------|--|--|--|--|--|

| K03 to K00                     | Input          | 4-bit input port                                                                                                  |                                  |  |  |  |  |  |

| P13 to P10                     | Output         | 4-bit output port with latch.                                                                                     |                                  |  |  |  |  |  |

| P20                            | Output         | 1-bit output port with latch.                                                                                     |                                  |  |  |  |  |  |

| R43 (AIN3)<br>to<br>R40 (AIN0) | l/O (Input)    | 4-bit I/O port with latch.<br>When using as input port, the latch must be set to "1".                             | AD converter analog input        |  |  |  |  |  |

| R71 (WTO)                      | I/O (Output)   | 1-bit I/O port with latch.<br>When using as input port or watchdog timer<br>output, the latch must be set to "1". | Watchdog timer output            |  |  |  |  |  |

| R82 (INT1)                     |                | 3-bit I/O port with latch.                                                                                        | External interrupt 1 input       |  |  |  |  |  |

| R81 (T2)                       | l/O (Input)    | When using as input port, external interrupt input pin, or timer / counter external input                         | Timer / Counter 2 external input |  |  |  |  |  |

| R80 (INT2)                     | -              | pin, the latch must be set to "1".                                                                                | External interrupt 2 input       |  |  |  |  |  |

| R92 (SCK)                      | I/O (I/O)      | 3-bit I/O port with latch.                                                                                        | Serial clock I/O                 |  |  |  |  |  |

| R91 (SO)                       | I/O (Output)   | When using as input port or serial port, the                                                                      | Serial data output               |  |  |  |  |  |

| R90 (SI)                       | I/O (Input)    | latch must be set to "1".                                                                                         | Serial data input                |  |  |  |  |  |

| XIN                            | Input          | Resonator connecting pin.                                                                                         |                                  |  |  |  |  |  |

| XOUT                           | Output         | For inputting external clock, XIN is used and X                                                                   | DUT is opened.                   |  |  |  |  |  |

| RESET                          | Input          | Reset/signal-input                                                                                                |                                  |  |  |  |  |  |

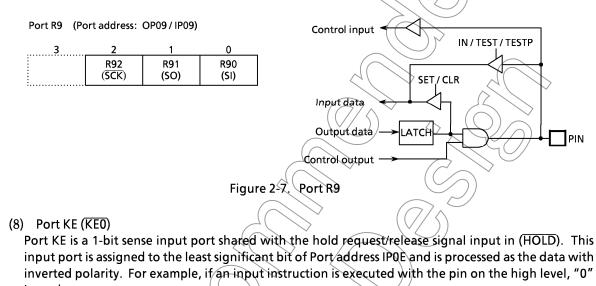

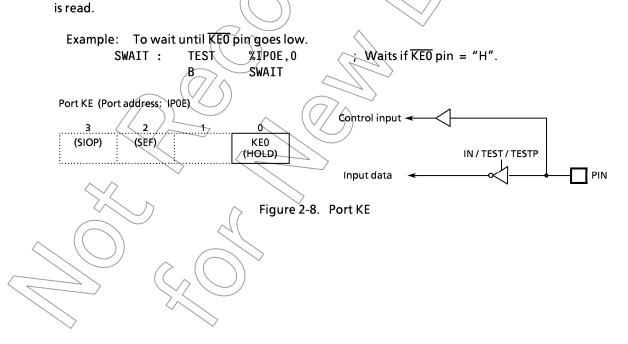

| HOLD (KEO)                     | Input (Input)  | HOLD request / release signatinput                                                                                | Sense input                      |  |  |  |  |  |

| TEST                           | Input          | Test pin for out-going test. Be opened or fixed                                                                   | to low level.                    |  |  |  |  |  |

| VDD                            |                | +5V                                                                                                               |                                  |  |  |  |  |  |

| VSS                            | Power supply   | 0 V (GND) AD converter analog reference<br>voltage (GND)                                                          |                                  |  |  |  |  |  |

| VAREF                          |                | AD converter analog reference voltage                                                                             |                                  |  |  |  |  |  |

# TOSHIBA

# **Operational Description**

Conserning the TMP47C241, the hardware configuration and operation are described. The configuration of basic machine instruction for TMP47C241 is same as TLCS-47 Series.

## 1. System Configuration

(1) Internal CPU Function

These as the same as the TMP47C203.

- (2) Peripheral Hardware Function

- I/O Ports

AD converter

Interval Timer

Watchdog Timer

Timer/Counters

Serial Interface

# 2. Peripheral Hardware Function

# 2.1 Ports

The TMP47C241 has 8 I/O ports (21 pins) each as follows:

| ••••                     |    | P • |                                                                             |

|--------------------------|----|-----|-----------------------------------------------------------------------------|

| 1                        | К0 | ;   | 4-bit input                                                                 |

| 2                        | P1 | ;   | 4-bit output                                                                |

| 3                        | P2 | ;   | 1-bit output                                                                |

| 4                        | R4 | ;   | 4-bitinput / output (shared by the AD converter analog inputs)              |

| 5                        | R7 | ;   | 1-bit input / output (shared by the watchdog timer output)                  |

| 6                        | R8 | ;   | 3-bit input / output shared by external interrupt request input and timer / |

|                          |    |     | counter input)                                                              |

| $\overline{\mathcal{O}}$ | R9 | ;   | 3-bit input / output (shared by serial port)                                |

| 8                        | KE | ;   | 1-bit sense input (shared by hold request / release signal input)           |

|                          |    |     |                                                                             |

5 pins (typ. 20 mA) of P1, P2 ports and 3pins (typ. 7 mA) of R9 port are high current output ports which can directly drive LEDs.

Table 2-3 lists the port address assignments and the I/O instructions that can access the ports. The 5-bit to 8-bit data conversion instruction [OUTB @HLbis invalid.

(1) Port K0 (K03 to K00) Port K0 is a 4-bit input-only port. A pull-up or pull-down resistor can be contained by the mask option.

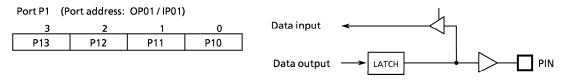

(2) Ports P1 (P13 to P10)

Ports P) is 4-bit high current output ports which can directly drive LEDs, with 4-bit latches. When an input instruction is executed, the latch data is read in these ports. The latch is initialized to "1" during reset.

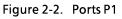

#### (3) Port P2 (P20)

Port P2 is 1-bit output port with latch. When used as an input port, the latch must be set to "1". The latch is initialized to "1" during reset. P21, P22 and P23pins do not exist actually. But these pins have the latches.

(4) Ports R4 (R43 to R40)

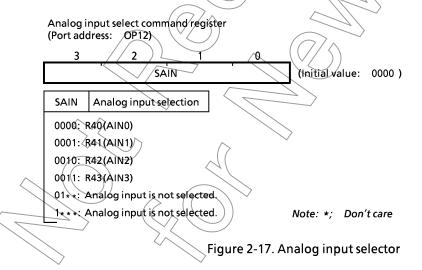

Ports R4 is 4-bit I/O ports with latch shared by the analog inputs for AD converter. When used as an input ports or analog inputs, the latch should be set to "1". If other port is used as an output, be careful not to execute the output instruction for any port during AD conversion in order to keep accuracy of conversion. The latch is initialized to "1" and analog input is selected R40 (AINO) pin during reset.

| Ро        | rt R4 (Po | rt address: C | )P04 / IP04)  | $\rightarrow$               | Analog input | selector          |     |

|-----------|-----------|---------------|---------------|-----------------------------|--------------|-------------------|-----|

| . <u></u> | 3         | 2             | 1 (( ))       | Analog input                | <u>√/_</u>   |                   | 1   |

|           | R43       | R42           | R41 R40       | ~                           | V T          | IN / TEST / TESTP |     |

|           | (AIN3)    | (AIN2)        | (AIN1) (AIN0) | Input data                  |              |                   | l l |

|           |           |               |               | Output data<br>2-4. Port R4 |              |                   | PIN |

#### (5) Port R7 (R71)

1-bit I/O pin with latch. R71 pin is shared by the watchdog timer output. To use R71 pin for the watchdog timer output, the latch should be set to "1". The latch is initialized to "1" during reset. R70, R72, R73 pins do not exist actually but R70 has the latch. In R72 and R73, "1" is read when an input instruction is executed.

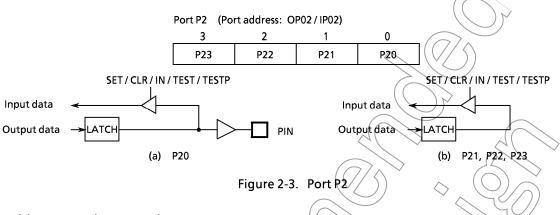

(6) Port R8 (R82 to R80)

3-bit I/O port with latch. When used as an input port, the latch must be set to "1". The latch is initialized to "1" during reset. R83 pins does not exist actually but R83 has the latch. There is no timer / counter 1 external input pin (T1).

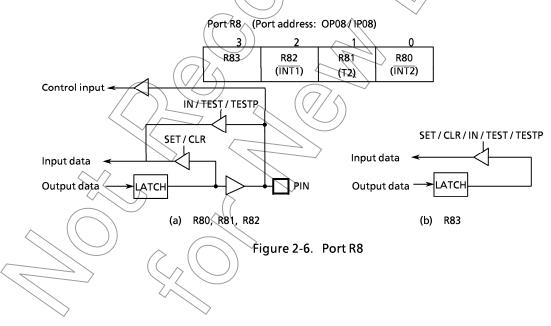

#### (7) Port R9 (R92 to R90)

Port R9 is a 3-bit I/O port with a latch. When used as an input, the latch must be set to "1". The latch is initialized to "1" during reset.

Port R9 is shared with the serial port. To use port R9 for the serial port, the latch should be set to "1". To use port R9 for an ordinary I/O port, the serial interface must be disabled.

Although R93 pin dose not exist actually, the set clear instruction for R93 ([SET % OP09, 3] or [CLR % OP09, 3]) should not be execution. However, other instructions can be used, in witch an undefined value is read upon execution of an input instruction.

|                                                         |                          |                             | 1                                                   |                              |          |                |     |                 |                                        |                        |                             |                          |                   |                        |               |                           |                                 | $\overline{\langle}$ | _                       |                         |                          | 7                                                                |

|---------------------------------------------------------|--------------------------|-----------------------------|-----------------------------------------------------|------------------------------|----------|----------------|-----|-----------------|----------------------------------------|------------------------|-----------------------------|--------------------------|-------------------|------------------------|---------------|---------------------------|---------------------------------|----------------------|-------------------------|-------------------------|--------------------------|------------------------------------------------------------------|

|                                                         |                          | SET @L<br>CLR @L<br>TEST @L |                                                     | 10                           | 110      |                |     |                 | 1                                      | I                      | 1                           |                          | I                 |                        |               | 1                         | I                               | 1                    |                         | $\neq$ )                |                          | >                                                                |

|                                                         |                          | TEST %p, b<br>TESTP %p, b   | 000                                                 | 10                           | 1   (    | 000            |     | 10              | 10                                     | 1                      |                             |                          | I                 | ı Ŷ                    |               |                           |                                 |                      |                         |                         |                          | -                                                                |

|                                                         | ction                    | SET %p, b<br>CLR %p, b      | 100                                                 | 10                           | (        | 000            |     |                 | 1                                      | I                      | 1                           |                          | -                 |                        |               |                           |                                 | 1                    |                         | I                       |                          |                                                                  |

| ctions                                                  | Input/Output instruction | OUTB @HL                    | 111                                                 |                              |          |                |     |                 | 1 1                                    | -                      |                             |                          |                   |                        |               | ł                         | ¢                               | + <                  |                         |                         | Z                        | $\left \right\rangle$                                            |

| ole I/O Instru                                          | Input/                   | OUT #k, %p                  | 100                                                 | 10                           | (        | 000            |     |                 |                                        | £/0//                  |                             |                          | >                 |                        |               | -                         |                                 |                      |                         | )                       | $\left \right $          |                                                                  |

| Port Address Assignments and Available I/O Instructions |                          | ОUT А,%р<br>ОUT @HL,%p      | 100                                                 | 10                           | 110      |                |     |                 |                                        | > 0                    |                             | Ŕ                        | 6                 | 10                     |               | $\langle \langle \rangle$ | /-<br>0                         | $\hat{\mathbf{y}}$   | C                       | 0                       | 10                       |                                                                  |

| Assignment                                              |                          | IN %p, A<br>IN %p, @HL      | 000                                                 | 10                           |          |                |     | )               | 00                                     | 0                      | _~_/                        |                          | 1                 |                        | $\bigvee_{i}$ | 1                         | I                               |                      | I                       | I                       | 1                        |                                                                  |

| ∑Table 2-1. Port Address                                | Port                     | Output (OP++)               | P1 output port<br>P2 output port                    | R4 output port               |          | R8 output port |     |                 |                                        | Serial transmit buffer | Hold operation mode control | AD analog input selector | AD start register | Watchdog Timer control |               | ļ                         | Interval Timer intrrupt control |                      | Timer/Counter 1 control | Timer/Counter 2 control | Serial interface control | available for the user programs.                                 |

|                                                         |                          | Input (IP**)                | K0 input port<br>P1 output latch<br>P2 output latch | R4 input port (Analog input) |          | R8 input port  |     | AD Status input | AD converted value<br>SIO, Hold status | Serial receive buffer  | Undefined                   | Undefined                | Undefined         | Undefined              | Undefined     | Undefined                 | Undefined                       | Undefined            | Undefined               | Undefined               | Undefined<br>Undefined   | "—" means the reserved state. Unavailable for the user programs. |

|                                                         | Port                     | Address<br>(**)             | 00 <sub>H</sub><br>01<br>02                         | 03                           | 05<br>06 | 0<br>80<br>00  | A O |                 | 0D<br>0E                               | ΟF                     | 10 <sub>H</sub>             | 12                       | ۳<br>۲            | 15                     | 16<br>17      | 18                        | 6                               | 4 I                  | ΞŲ                      | 10                      | Щ Ц                      | Note: "                                                          |

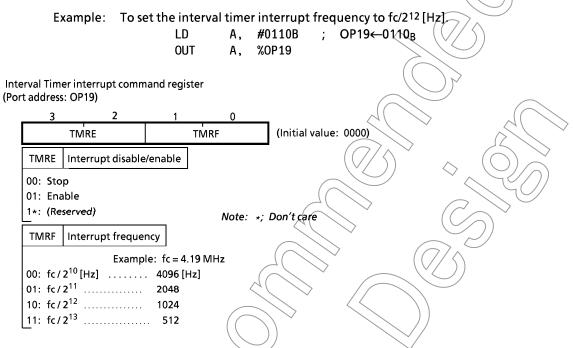

#### 2.2 Interval Timer Interrupt (ITMR)

The interval timer can be used to generate an interrupt with a fixed frequency. Internal time interrupt is control by the command register (OP19). An interval timer interrupt is generated at the first rising edge of the binary counters output after the command has been set. The interval timer is not cleared by command, so that the first interrupt may occur earlier than the preset interrupt period.

#### Figure 2-9. Interval Timer Interrupt Command Register

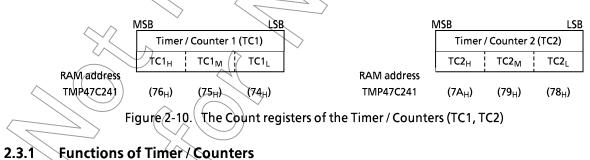

# 2.3 Timer/Counters (TC1, TC2)

The TMP47C241 contain two 72-bit timer/counters (TC1, TC2). RAM addresses are assigned to the count register in unit of 4 bits, permitting the initial value setting and counter reading through the RAM manipulation instruction. When the timer/counter is not used, the mode selection may be set to "stopped" to use the RAM at the address corresponding to the timer / counter for storing the ordinary user-processed data.

The timer / counters provide the following functions:

- ① Event counter

- ② Programmable timer

- ③ Pulse width measurement

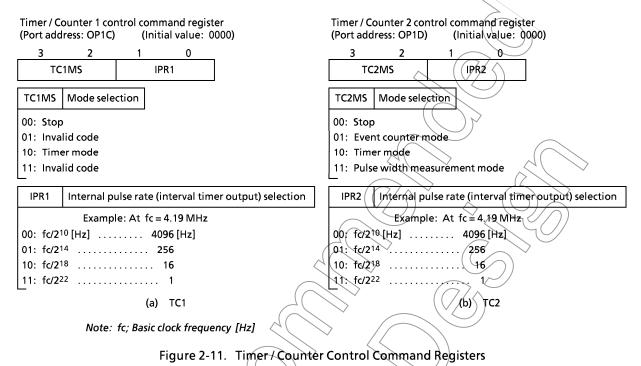

#### 2.3.2 Control of Timer / Counters

The timer / counters are controlled by the command registers. The command register is accessed as port address OP1C for TC1 and port address OP1D for TC2. These registers are initialized to "0" during reset.

The timer/counter increments at the rising edge of each count pulse. Counting starts with the first rising edge of the count pulse generated after the command has been set. Count operation is performed in one instruction cycle after the current instruction execution, during which the execution of a next instruction and the acceptance of an interrupt are delayed. If counting is requested by both TC1 and TC2 simultaneously, the request by TC1 is preferred. The request by TC2 is accepted in the next instruction cycle. Therefore, during count operation, the apparent instruction execution speed drops as counting occurs more frequently.

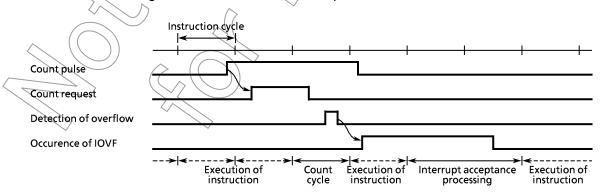

The timer / counter causes an interrupt upon occurrence of an overflow (a transition of the count value from  $FFF_H$  to  $000_H$ ). If the timer / counter is in the interrupt enabled state and the overflow interrupt is accepted immediately after its occurrence, the interrupt is processed in the sequence shown in Figure 2-12. Note that counting continues if there is a count request after overflow occurrence.

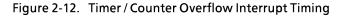

#### (1) Event counter mode

In the event counter mode, the timer / counter increments at each rising edge of the external pin (T1, T2) input. T1 and T2 pins are also used as the R83 and R81 pins.

To use these pins as the T/C input, set the output latch of R83 and R83 and R81 to "1".

At reset, the output latch is initialized to "1". The maximum applied frequency of the external pin input is fc/32 for the 1-channel operation; for the 2-channel operation, the trequency is fc/32 for TC1 and fc/40 for TC2. The apparent instruction execution speed drops most to  $(9/11) \times 100 = 82\%$  when TC1 and TC2 are operated at the maximum applied frequency because the count operation is inserted once every 4 instruction cycles for TC1 and every 5 cycles for TC2. For example, the instruction execution speed of 2  $\mu$ s drops to 3.64  $\mu$ s.

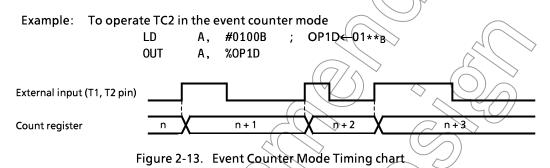

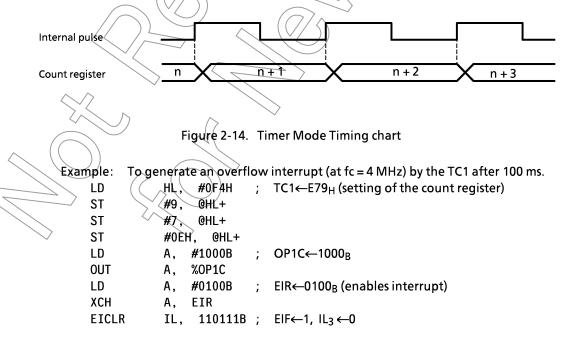

(2) Timer mode

In the timer mode, the timer/counter increments at the rising edge of the internal pulse generated from the interval timer. One of 4 internal pulse rates can be selected by the command register. The selected rate can be initially set to the timer/counter to generate an overflow interrupt in order to create a desired time interval.

When an internal pulse rate of  $fc/2^{10}$  is used, a count operation is inserted once every 128 instruction cycles, so that the apparent instruction execution speed drops by (1/127) × 100 = 0.8 %. For example, the instruction execution speed of 2  $\mu$ s drops to 2.016  $\mu$ s.

In the timer mode, R83 (T1), and R81 (T2) pins provide the ordinary I/O ports.

#### \* Calculating the preset value of the counter register

The preset value of the count register is obtained from the following relation:

$2^{12}$  – (interrupt setting time)  $\times$  (internal pulse rate)

For example, to generate an overflow interrupt after 100 ms at fc = 4 MHz with the internal pulse rate of  $fc/2^{10}$ , set the following value to the count register as the preset value:

} × 100

[%]

$2^{12}$  - (100 × 10<sup>-3</sup>) × (4 × 10<sup>6</sup>/2<sup>10</sup>) = 3705 = E79<sub>H</sub>

\* The apparent execution rate is calculated as following.

| Internal pulse rate     | Max. setting time       | Example: At fc = 4.194304 MHz<br>Internal pulse rate Max. setting time |

|-------------------------|-------------------------|------------------------------------------------------------------------|

| fc/2 <sup>10</sup> [Hz] | 2 <sup>22</sup> /fc [s] | 4096 [Hz] 1 [s]                                                        |

| fc/2 <sup>14</sup>      | 2 <sup>26</sup> /fc     | 256 16                                                                 |

| fc/2 <sup>18</sup>      | 2 <sup>30</sup> /fc     | 16 256                                                                 |

| fc/2 <sup>22</sup>      | 2 <sup>34/fc</sup>      | 4096                                                                   |

Table 2-2. Internal Pulse Rate Selection

(3) Pulse width measurement mode

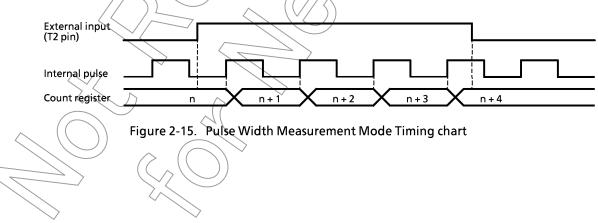

In the pulse width measurement mode, the timer / counter increments with the pulse obtained by sampling the external pin (T1, T2) by the internal pulse. As shown in Figure 2-15, the timer / counter increments only while the external pin input is high. The maximum applied frequency to the external pin input must be one that is enough for analyzing the count value. Normally, a frequency sufficient slower than the internal pulse rate setting is applied to the external pin.

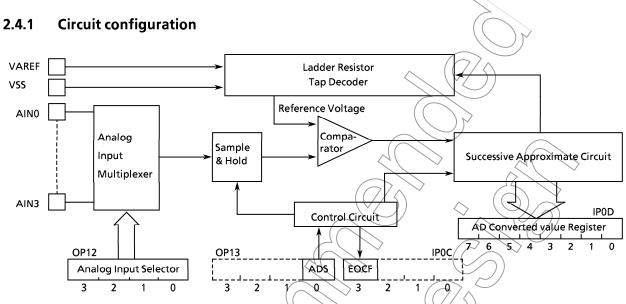

## 2.4 AD Converter

The TMP47C241 has a 8-bit successive approximate type AD converter and is capable of processing 4 analog inputs.

Figure 2-16. Block Diagram of AD Converter

#### 2.4.2 Control of AD converter

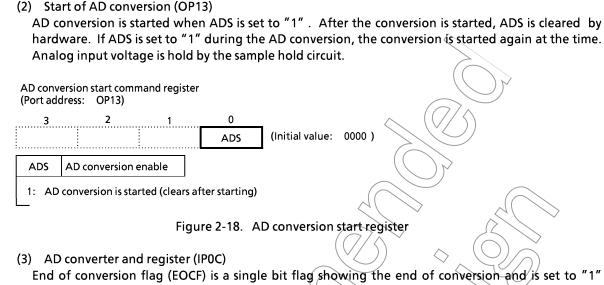

The operation of AD converter is controlled by a command register (QP12, OP13, IPOC, IPOD).

(1) Analog input selector (OP12) Analog inputs (AIN0 through AIN3) are selected by values of this register.

End of conversion flag (EOCF) is a single bit flag showing the end of conversion and is set to "1" when conversion ended. When both upper 4 bits and lower 4 bits of a converted value are read or AD conversion is started, EOCF is cleared to "0".

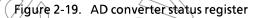

AD converter status register (Port address: IP0C)

| 3    | 2 | 1 | 0 < |

|------|---|---|-----|

| EOCF |   |   |     |

|      |   |   |     |

EOCF End of conversion flag

- 0: Under AD conversion or before AD conversion

- 1: End of AD conversion

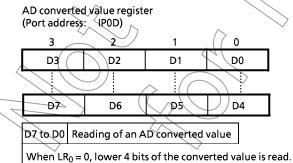

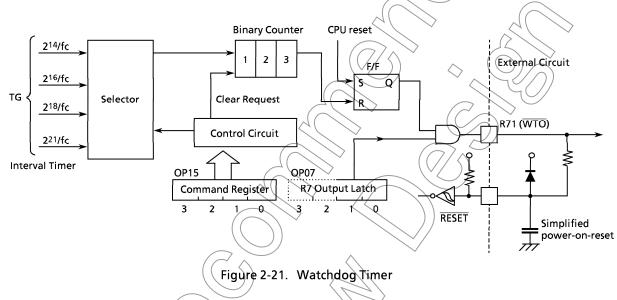

(4) AD converted value register (IP0D)

An AD converted value is read by accessing port address IP0D. An AD converted value is read by splitting into upper 4 bits and lower 4 bits by a value of LR<sub>0</sub> (LSB of the L-registers).

When  $LR_0 = 0$ , lower 4 bits of the converted value is read. When  $LR_0 = 1$ , upper 4 bits of the converted value is read.

#### 2.4.3 How to use AD converter

Apply positive of analog reference voltage to the VAREF pin and negative to the VSS pin. The AD conversion is carried out by splitting reference voltage between VAREF and VSS to bit corresponding voltage by a ladder resistor and making a judgement by comparing it with analog input voltage.

Analog supply current (I<sub>REF</sub>) is typically 500  $\mu$ A at VAREF = 5 V.

Note that this ladder resistor is connected to VAREF and VSS even in the HOLD mode. Therefore to reduce the power consumption, VAREF should be disconnected from the analog reference voltage supply.

(1) Start of AD conversion

Prior to conversion, select one of the analog input AIN0 through AIN3 by the analog input selector. Place output of the analog input, which is to be AD converted, in the high impedance state by setting "1". If other port is used as an output, be careful not to execute the output instruction for any port during conversion in order to keep accuracy of conversion.

AD conversion is started by setting ADS (bit 1 of the AD conversion start register). When conversion ends after 24 instruction cycles, EOCF showing the end of conversion is set to "1".)

Analog input voltage is sampled during the following 2 instruction cycles after setting ADS.

Note: The sample and hold circuit has capacitor ( $C_A = 12 \text{ pF}$  typ.) with resistor ( $R_A = 5 \text{ k}\Omega$  typ.). See I/O circuitry table. This capacitor should be charged or discharged within 2 instruction cycles.

(2) Reading of an AD converted value

After the end of conversion, read an AD converted value is read by splitting into lower 4 bits and upper 4 bits by the AD converted value register (IPOD).

Lower 4 bits of the AD converted value can be read when  $LR_0 = 0$  and upper 4 bits when  $LR_0 = 1$ . Usually an AD converted value is stored in RAM by an instruction [IN %p, @HL]. Further, if an AD converted value is read during the conversion, it becomes an indefinite value.

# (3) AD conversion with HOLD operation

When the HOLD operation is started during the conversion, the conversion is terminated and an AD converted value becomes indefinite. Therefore, EOCF is kept clear to "0" after release from the HOLD operation. However, if the HOLD operation is started after the end of AD conversion (after EOCF has been set), AD converted value and status of EOCF are held.

Example: Selecting analog input (AIN3), starting AD conversion, monitoring EOCF and storing lower 4 bits and upper 4 bits of a converted value to RAM [10<sub>H</sub>] and RAM [11<sub>H</sub>]

| respectiv | /ely.  |            |   |                                       |

|-----------|--------|------------|---|---------------------------------------|

| ZA N      | LD 🔨   | A, #3 💛    | ; | Selects analog input (AIN3)           |

| Č V       | OUT (/ | A, %OP12   |   |                                       |

|           |        | A, #1      | ; | Start of AD conversion                |

|           | OUT    | A, %0P13   |   |                                       |

| SLOOP :   | TE\$T  | %IPOC, 3   | ; | To wait until EOCF goes to "1"        |

|           | ∕B∖∕∕  | SLOOP      |   |                                       |

|           | ΈQ 🔨   | HL, #10H   | ; | HL ← 10 <sub>H</sub>                  |

|           | ÌN     | %IPOD, @HL | ; | RAM [10 <sub>H</sub> ] ← Lower 4 bits |

| $\sim$    | INC    | L          | ; | Increment of L registers              |

|           | IN     | %IPOD, @HL | ; | RAM [11 <sub>H</sub> ] ← Upper 4 bits |

|           |        |            |   |                                       |

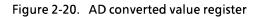

# 2.5 Watchdog Timer (WDT)

The purpose of the watchdog timer is to detect the malfunction (ranaway) of program due to external noise or other causes and return the operation to the normal condition.

The watchdog timer output is output to R71 must be set to "1". Further, during reset, the output latch of R71 is set to "1", and the watchdog timer becomes disable state.

The initialization at time of runaway will become possible when the WTO pin and RESET pin are connected each other.

# 2.5.1 Configuration of Watchdog Timer

The watchdog timer consists of 3-stage binary counter, flip-flop (F/F), and its control circuit. The F/F is set to "1" during reset, and cleared to "0" at the rising edge of the binary counter output.

# 2.5.2 Control of watchdog/timer

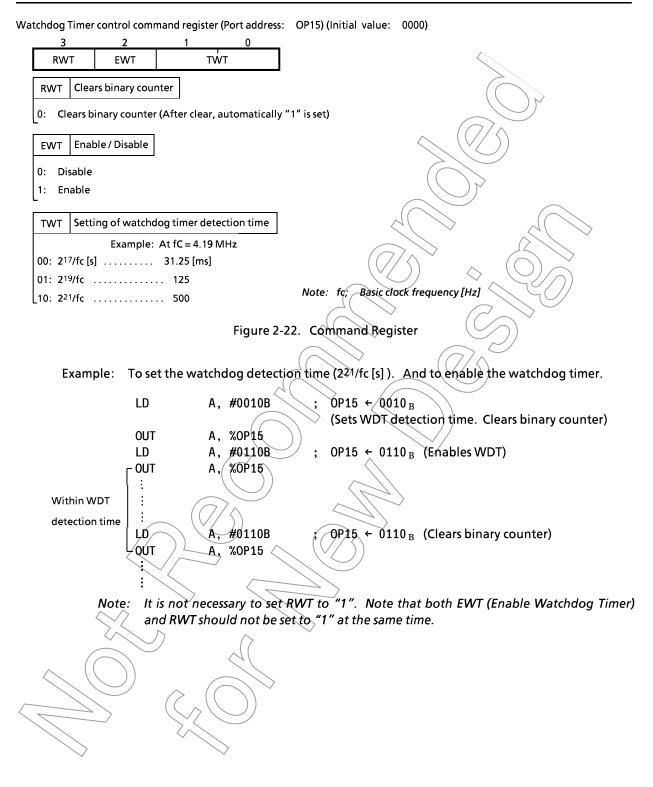

The watchdog timer is controlled by the command register (OP15). This command register is initialized to " $0000_B$ " during reset. The following are procedure to detect the malfunction (runaway) of CPU by the watchdog timer.

- 1 At first, detection time of the watchdog timer should be set and binary counter should be cleared.

- ② The watchdog timer should be become enable.

- ③ Binary counter must be cleared before the detection time of the watchdog timer. When the runaway of CPU is taken place for some reason and binary counter is not cleared, the F/F is cleared to "0" at the rising edge of the binary counter and signal of runaway detection is become active (WTO output is "L").

# TOSHIBA

# TOSHIBA

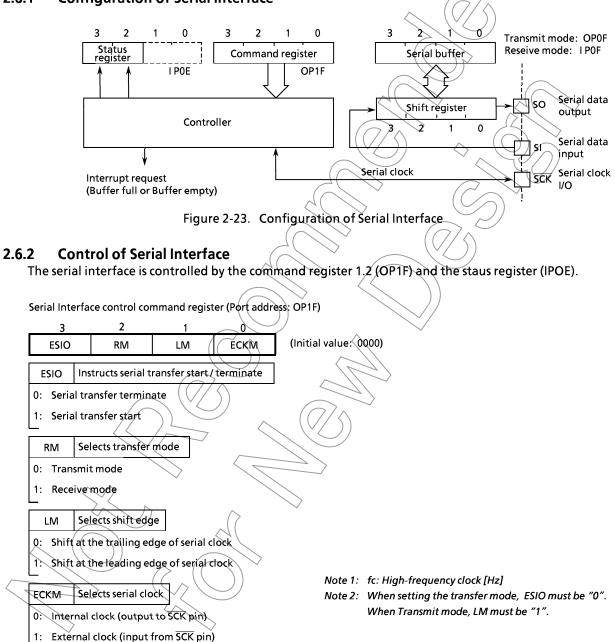

# 2.6 Serial Interface (SIO)

The TMP47C200B/400B have a serial interface with a 4-bit buffer. The serial interface is connected to the external device via 3 pins (the serial port): R92 (SCK), R91 (SO), and R90 (SI). The serial port is shared by port R9. For the serial port, the output latch of port R9 must be set to "1". In the transmit mode, R90 pin provides the I/O port; in the receive mode, R91 pin provides the I/O port.

# 2.6.1 Configuration of Serial Interface

Serial Interface status register (Port address: IPOE)

| 3                                |                                          | 2                                 | 1             | 0      |  |  |  |  |  |

|----------------------------------|------------------------------------------|-----------------------------------|---------------|--------|--|--|--|--|--|

| SIO                              | F                                        | SEF                               | (SMF)         | (HOLD) |  |  |  |  |  |

| SIOF                             | Monitors serial transfer operation state |                                   |               |        |  |  |  |  |  |

| 0: Transfer is terminated        |                                          |                                   |               |        |  |  |  |  |  |

| 1: Tra                           | Insfer                                   | is in progress                    | 5             |        |  |  |  |  |  |

| SEF                              | SEF Monitors shift operation state       |                                   |               |        |  |  |  |  |  |

| 0: Shift operation is terminated |                                          |                                   |               |        |  |  |  |  |  |

| 1: Tra                           | nsfer<br>Mor                             | is in progress<br>nitors shift op | eration state | ]      |  |  |  |  |  |

1: Shift operation is in progress

#### Figure 2-25. Serial Interface Status Register

#### 2.6.3 Serial Clock

For the serial clock, one of the following can be selected according to the contents of the command register:

- (1) Clock source selection

- a. Internal clock

fc/27 [Hz] is used for the serial clock (at fc = 4/194304 MHz, the serial clock frequency is 32.768 kHz). The serial clock is output on the SCK pin. Note that at the start of transfer, the  $\overline{SCK}$  pin output goes high. This serial interface provides the wait function in which the shift is not occurred until these processings are completed.

The highest transfer rate based on the internal clock is 31250 bits/second (at fc = 4 MHz).

b. External clock

The signal obtained by the clock supplied to the  $\overline{SCK}$  pin from the outside is used for the serial clock. In this case, the output latch of R92 (SCK) must be set to "1" beforehand. For the shift operation to be performed correctly, each of the clock's high and low levels needs two instructions or more to be completed.

#### (2) Shift edge selection

a. Leading edge

Data is shifted at the leading edge (the falling edge of SCK pin input) of the serial clock. b. Trailing edge

Data is shifted at the trailing edge (the rising edge of SCK pin input) of the serial clock. However, in the transmit mode, the trailing edge shift is not supported.

# 2.6.4 Transfer Modes

Selection between the transmit mode and the receive mode is performed by RM (bit 2 of the command register).

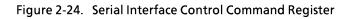

#### (1) Transmit mode

The transmit mode is set to the command register then the first transmit data (4 bits) is written to the buffer register OPOF (if the transmit mode is not set, the data is not written to the buffer register). Then, setting ESIO to "1" starts transmission. The transmit data is output to the SO pin synchronization with the serial clock from the LSB side sequentially. When the LSB is output, the transmit data is moved from the buffer register to the shift register. When the buffer register becomes empty, the buffer empty interrupt (ISIO) to request for the next transmit data is generated. When the interrupt service program writes the transmit data to the buffer register, the interrupt request is reset. In the operation based on the internal clock, if no more data is set after the transmission of the 4-bit data, the serial clock is stopped and the wait state sets in.

In the operation based on the external clock, the data must be set in the buffer register by the time the next data shift operation starts. Therefore, the transfer rate is determined by the maximum delay time between the occurrence of the interrupt request and the writing of data to the buffer register by the interrupt service program.

To end transmission, ESIO is cleared to "0" instead of writing the next transmit data by the buffer empty interrupt service program. When ESIO is cleared, transmission stops upon termination of the currently shifted-out data. The transmission end can be known by the SIOF state (SIOF goes "0" upon transmission end). In the operation based on the external clock, ESIO must be cleared to "0" before the next data is shifted out. If ESIO is not cleared before, the transmission stops upon transmitting the next data (dummy).

Example 1: To transmit data stored in the RAM (its address is specified by the HL register pair) in synchronization with the internal clock. LD A, #0010B ; OP1F $\leftarrow$ 0010<sub>B</sub> (Sets the transmit mode of

|     |            | internal-clock-based operation)                  |

|-----|------------|--------------------------------------------------|

| OUT | A, %OP1F   |                                                  |

| OUT | @HL, %OPOF | ; OP0F←RAM [HL] (Writes the first transmit data) |

| LD  | A, #1010B  | ; ESIO←1 (Instructs transmission start)          |

| OUT | A, %OP1F   | $\langle (\sqrt{5})$                             |

To end transmission (internal-clock-based operation) Example 2: A #0010P I D

; ESIO←0 (Instructs transmission end)

|        | LD    | A, #0010D |                          |

|--------|-------|-----------|--------------------------|

|        | OUT   | A, %OP1F  |                          |

| SENDC: | TESTP | %IP0E, 3  | ; Waits until SIQF = "0" |

|        | В     | SENDC     |                          |

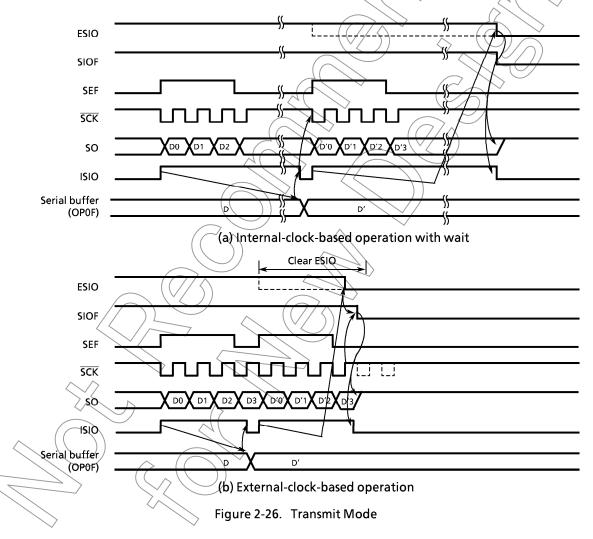

(2) Receive mode

Data can be received when ESIO is set to "1" after setting the receive mode to the command register. The data is put from the SI pin to the shift register in synchronization with the serial clock. Then the 4-bit data is transferred from the shift register to the buffer register (IPOF), upon which the buffer full interrupt (ISIO) to request for reading received data is generated. The received data is read from the buffer register by the interrupt service program. When the data has been read, the interrupt request is reset and the next data is put in the shift register to be transferred to the buffer register,

In the operation based on the internal clock, if the previous received data has not been read from the buffer register at the end of capturing the next data, the serial clock is stopped and the wait operation is performed until the data has been read.

In the operation based on the external clock, the shift operation is performed in synchronization with the externally-supplied clock, so that the data must be read from the buffer register before the next receive data is transferred to it. The maximum transfer rate in the external-clock-based operation is determined by the maximum delay time between the generation of interrupt request and the reading of received data.

In the receive mode, the shift operation may be performed at either the leading edge or the trailing edge. In the leading edge shift operation, data is captured at the leading edge of the serial clock, so that the first shift data must be put in the SI pin before the first serial clock is applied at the start of transfer.

Note: If the transfer modes are changed, the contents of the buffer register are lost.

Therefore, the modes should not be changed until the last received data is read even after the end of reception is instructed (by clearinf ESIO to "0").

Example: To instruct the receive start operation with the internal clock and leading edge shift (with the interrupt enable register already set).

| LD A,#01                         | $OP1F \leftarrow 0110_B$ (Sets the receive mode)              |

|----------------------------------|---------------------------------------------------------------|

| EI<br>LD A,#11<br>OUT A,%0F<br>: | EIF←1 (Enables interrupt)<br>ESIO←1 (Instructs receive start) |

To end the receive operation, ESIO should be cleared to "0". When ESIO is cleared, the completion of the transfer of the current 4-bit data to the buffer register terminates the receive operation. To confirm the end of the receive operation by program, SIOF should be sensed. SIOF goes "0" at the end of receive operation.

Note: If the receive and transmit modes are switched, the contents of the buffer register are lost. Therefore, the modes should not be switched until the last receive data is read even after the end of reception is instructed (by clearing ESIO to "0").

The receive operation can be terminated in one of the following approaches determined by the transfer rate:

a. When the transfer rate is sufficiently low (the external-clock-based operation): If ESIO can be cleared to "0" before the next serial clock is applied upon occurrence of buffer full interrupt in the external-clock-based operation, ESIO is cleared to "0" by the interrupt service program, then the last receive data is read.

Example: To instruct the receive end with sufficient low transfer rate (the reading edge shift).

| LD  | A,#0111B | ; | ESIO←0 (Instructs receive end) |

|-----|----------|---|--------------------------------|

| OUT | A,%OP1F  |   |                                |

| IN  | %IPOF,A  | ; | AccelPOF (Reads received data) |

b. When the transfer rate is sufficiently high (the internal/external clock-based operation): If the transfer rate is high and, therefore, it is possible that the capture of the next data starts before ESIO is cleared to "0" upon acceptance of an interrupt, ESIO must be cleared to "0" by confirming that SEF (bit 2 of the status register) is set at reading the data proceeding the last data. Then, the data is read.

In the interrupt servicing following the reception of the last data, no operation is needed for termination; only the reading of the received data is performed. This method is generally employed for the internal-clock-based operations. For an external-clock-based operation, ESIO must be cleared and the receive data must be read before the last data is transferred to the buffer register.

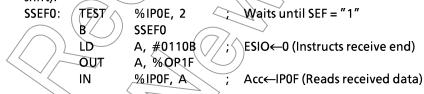

Example: To instruct receive end when the transfer rate is high (the internal clock, reading edge shift).

c. One-word reception

When receiving only one word, ESIO is set to "1" then it is returned to "0" after confirming that SEF (bit 2 of the status register) has gone "1". In this case, buffer full interrupt is caused only once, so that the received data is read by the interrupt service program.

To instruction the start/end of one-word reception (the internal clock, the leading edge shift).

| eugesii      | LD   | A, #0110B | ; | $OP1F \leftarrow 0110_B$ (Sets in the receive mode) |

|--------------|------|-----------|---|-----------------------------------------------------|

| $\checkmark$ | QUI  | A, %OP1F  |   |                                                     |

|              | EI   |           | ; | EIF←1 (Enables interrupt)                           |

|              | LD   | A, #1110B | ; | ESIO←1 (Instructs receive start)                    |

|              | OUT  | A, %OP1F  |   |                                                     |

| SSEF0:       | TEST | %IP0E, 2  | ; | Confirms that SEF = "1"                             |

|              | В    | SSEFO     |   |                                                     |

|              | LD   | A, #0110B | ; | ESIO←0 (Instructs receive end)                      |

|              | OUT  | A, %OP1F  |   |                                                     |

|              |      |           |   |                                                     |

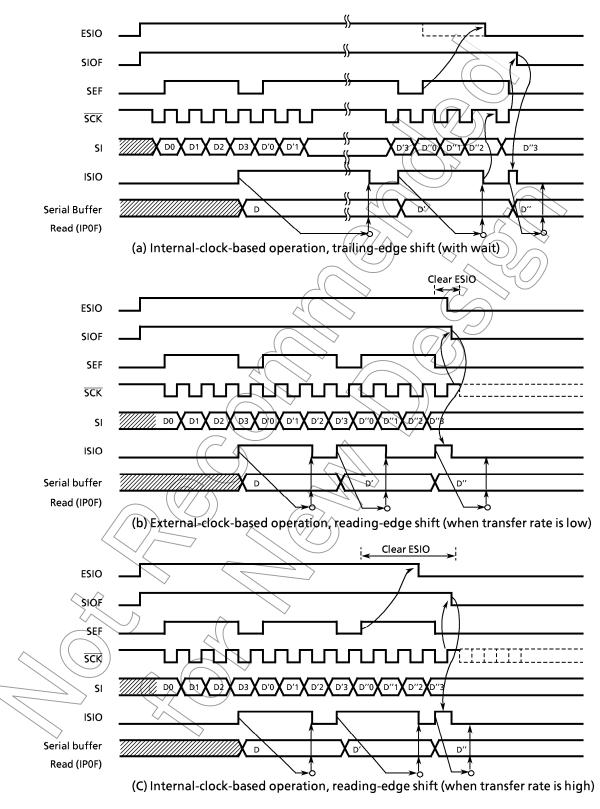

Figure 2-27. Receive Mode

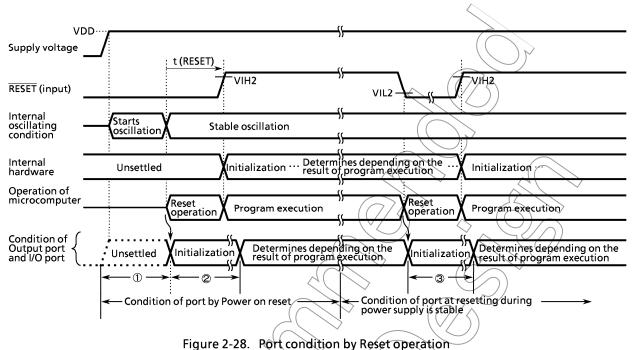

## Port Condition by RESET Operation

The transition of Port condition by RESET operation is shown as below.

- Note 1: t (RESET) > 24/fc

- Note 2: VIL2: Stands for low level input voltage of RESET pin. VIH2: Stands for high level input voltage of RESET pin.

- Note 3: The condition of each port is unstable until the reset operation is started (① in the above Figure). Thus, when using port as an output pin, in the term of ①, to prevent the malfunction of external application circuit, insert the circuit outside of microcomputer between the output pin of Port and input pin of external application circuit.

- Note 4: The term starting from reset operation to the program which accesses port is executed (2, 3 in the above Figure), the condition of port becomes on the status of initialization by Reset operation. The initial condition of port differs from I/O circuit by each port, refer to the section of "INPUT/OUTPUT CIRCUITRY". Thus, when using Port as an output pin, in the term of the above 2 and 3, the voltage level on the signal that connects with the output pin of Port to the input pin of external application circuit should be determined by the external circuitry such as pull-up resistor and/or pull-down resistor.

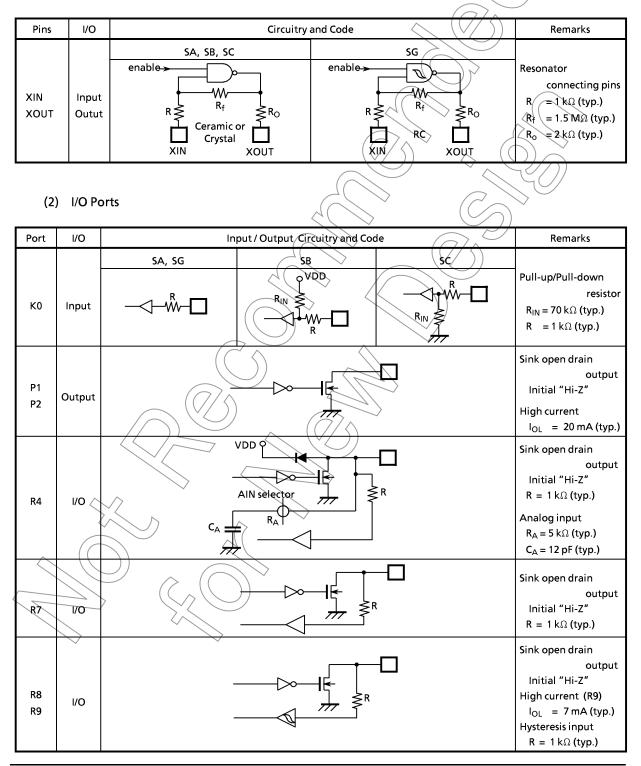

## Input / Output Circuitry

The input / output circuitries of the TMP47C241 (code SA-SC or SG) are shown as below.

(1) Control pins

The input / output circuitries of the TMP47C241 control pins except XIN and XOUT pins are similar to that of the TMP47C200B.

## **Electrical Characteristics**

| Absolute Maximum Ratings        | (V <sub>SS</sub> = ) | ע ט(                       |                                |      |  |

|---------------------------------|----------------------|----------------------------|--------------------------------|------|--|

| Parameter                       | Symbol               | Pins                       | Ratings                        | Unit |  |

| Supply Voltage                  | V <sub>DD</sub>      |                            | =0.3 to 7                      | V    |  |

| Input Voltage                   | V <sub>IN</sub>      | $\sim$ (7)                 | 0.3 to V <sub>DD</sub> + 0.3   | V    |  |

|                                 | V <sub>OUT1</sub>    | Except sink open drain pin | -0.3 to V <sub>DD</sub> + 0.3  |      |  |

| Output Voltage                  | V <sub>OUT2</sub>    | Ports P1, P2, R7 to R9     | – 0.3 to 10                    | V    |  |

|                                 | V <sub>OUT3</sub>    | Analog inputs              | – 0.3 to V <sub>DD</sub> + 0.3 |      |  |

|                                 | I <sub>OUT1</sub>    | Ports P1, P2               | 30                             |      |  |

| Output Current (Per 1 pin)      | I <sub>OUT2</sub>    | Port R9                    | 1/5                            | mA   |  |

|                                 | I <sub>OUT3</sub>    | Ports R4, R7, R8           | 3.2                            |      |  |

| Output Current (Total)          | $\Sigma I_{OUT1}$    | Ports P1, P2, R9           | 120                            | mA   |  |

| Power Dissipation [Topr = 70°C] | PD                   |                            | 300                            | mW   |  |

| Soldering Temperature (time)    | Tsld                 |                            | 260(10,5)                      | °C   |  |

| Storage Temperature             | Tstg                 |                            | - 55 to 125                    | °C   |  |

| Operating Temperature           | Topr                 |                            | - 30 to 70                     | °C   |  |

Note: The absolute maximum ratings are rated values which must not be exceeded during operation, even for an instant. Any one of the ratings must not be exceeded. If any absolute maximum rating is exceeded, a device may break down or its performance may be degraded, causing it to catch fire or explode resulting in injury to the user. Thus, when designing products which include this device, ensure that no absolute maximum rating-value will ever be exceeded.

(Vss =)0 V, Topr = - 30 to 70°C)

| Parameter          | Symbol            | Pins                      | Conditions                       | Min                   | Max                    | Unit  |

|--------------------|-------------------|---------------------------|----------------------------------|-----------------------|------------------------|-------|

|                    |                   |                           | (te=6:0 MHz                      | 4.5                   |                        | ĺ     |

| Supply Voltage     | VDD               | 77                        | fc = 4.2  MHz                    | 2.7                   | 6.0                    | v     |

|                    | > (               | $( \langle \rangle )$     | In the HOLD mode                 | 2.0                   |                        |       |

|                    | VIH1              | Except Hysteresis Input ( | n the normal                     | $V_{DD} \times 0.7$   |                        |       |

| Input High Voltage | /V <sub>1H2</sub> | Hysteresis Input          | operating area                   | $V_{DD} \times 0.75$  | V <sub>DD</sub>        | V     |

|                    | ू (VIH3           |                           | In the HOLD mode                 | V <sub>DD</sub> × 0.9 |                        |       |

|                    | V <sub>IL1</sub>  | Except Hysteresis Input   | In the normal                    |                       | V <sub>DD</sub> × 0.3  |       |

| Input Low Voltage  | V <sub>IL2</sub>  | Hysteresis Input          | operating area                   | 0                     | V <sub>DD</sub> × 0.25 | V     |

|                    | V <sub>IL3</sub>  |                           | In the HOLD mode                 |                       | V <sub>DD</sub> × 0.1  |       |

|                    | )                 | $\wedge$                  | V <sub>DD</sub> = 4.5 V to 6.0 V |                       | 6.0                    |       |

| Clock Frequency    | fc                | $\triangleleft$           | V <sub>DD</sub> = 2.7 V to 6.0 V | 0.4                   | 4.2                    | ] MHz |

| $\land (())$       |                   |                           | In the RC oscillation            |                       | 2.5                    |       |

**Recommended Operating Conditions**

The recommended operating conditions for a device are operating conditions under which it can be guaranteed that Note: the device will operate as specified. If the device is used under operating conditions other than the recommended operating conditions (supply voltage, operating temperature range, specified AC/DC values etc.), malfunction may occur. Thus, when designing products which include this device, ensure that the recommended operating conditions for the device are always adhered to.

| DC Characteristics                     |                  | $V_{SS} = 0 V$ , Topr = $-30 \text{ to } 70^{\circ}\text{C}$ |                                                        |                  |              |     |      |  |

|----------------------------------------|------------------|--------------------------------------------------------------|--------------------------------------------------------|------------------|--------------|-----|------|--|

| Parameter                              | Symbol           | Pins                                                         | Conditions                                             | Min              | тур.         | Max | Unit |  |

| Hysteresis Voltage                     | V <sub>HS</sub>  | Hysteresis Input                                             |                                                        |                  | 0.7          | —   | v    |  |

| Input Current                          | I <sub>IN1</sub> | Port K0, TEST,<br>RESET, HOLD                                | V <sub>DD</sub> = 5.5V,<br>V <sub>IN</sub> = 5.5V / 0V |                  | _            | ± 2 | μΑ   |  |

|                                        | I <sub>IN2</sub> | Ports R (open drain)                                         |                                                        | 7                |              |     |      |  |

| Input Posistance                       | R <sub>IN1</sub> | Port K0 with pull-up/pull-down                               |                                                        | 30               | 70           | 150 | kΩ   |  |

| Input Resistance                       | R <sub>IN2</sub> | RESET                                                        |                                                        | 100              | 220          | 450 | K77  |  |

| Output Leakage Current                 | I <sub>LO</sub>  | Ports R, P (open drain)                                      | V <sub>DD</sub> = 5.5 V, V <sub>OUT</sub> = 5.5 V      | - (              |              | 2   | μA   |  |

| Output Low Voltage                     | V <sub>OL2</sub> | Except XOUT, ports P                                         | $V_{DD} = 4.5 V / I_{OL} = 1.6 \text{ mA}$             |                  | $\mathbb{R}$ | 04  | v    |  |

| Low Output Current                     | I <sub>OL1</sub> | Ports P1, P2                                                 | $V_{DD} = 4.5 V, V_{OL} = 1.0 V$                       | L<br>L           | 20           | ٧_  | mA   |  |

| Low Output current                     | I <sub>OL2</sub> | Port R9                                                      | $v_{DD} = 4.3 v, v_{OL} = 1.0 v$                       |                  | 7            | _   |      |  |

|                                        |                  |                                                              | $V_{DD} = 5.5 V, fc = 410Hz$                           | $\mathbb{Y}_{<}$ | 2            | 4   |      |  |

| Supply Current<br>(in the Normal mode) | I <sub>DD</sub>  |                                                              | $V_{DD} = 3.0 V$ , fc = 4 MHz                          | ))-              | 1            | 2   | mA   |  |

| ,,                                     |                  |                                                              | $V_{DD} = 3.0 V, fc = 400 \text{ kHz}$                 | _                | 0.5          | 1   |      |  |

| Supply Current<br>(in the HOLD mode)   | I <sub>DDH</sub> |                                                              | V <sub>DD</sub> = 5.5 V                                | _                | 0.5          | 10  | μA   |  |

DC Characteristics

$(V_{SS} = 0 V, Topr = -30 to 70^{\circ}C)$

Note 1: Typ. values show those at Topr =  $25^{\circ}$ ,  $V_{DD} = 5 \cdot V$ .

Note 2: Input Current I<sub>IN1</sub>; The current through resistor is not included, when the input resistor (pull-up/pull-down) is contained.

Note 3: Supply Current I<sub>DD</sub>, I<sub>DDH</sub> ;  $V_{IN} = 5.3 V/0.2 V (V_{DD} = 5.5 V), 2.8 V/0.2 V (V_{DD} = 3.0 V)$

AD Conversion Characteristics (Topr ⊨ – 30 to 70°C)

|                                |                   |                                     | 1                     |      |                   |      |

|--------------------------------|-------------------|-------------------------------------|-----------------------|------|-------------------|------|

| Parameter                      | Symbol            | Conditions                          | Min                   | Тур. | Max               | Unit |

| Analog Reference Voltage       | VAREF             | $\searrow$                          | V <sub>DD</sub> – 1.5 | Ι    | V <sub>DD</sub>   | v    |

| Analog Reference Voltage Range |                   | V <sub>AREF</sub> – V <sub>SS</sub> | 2.7                   | Ι    | -                 | v    |

| Analog Input Voltage           | VAIN              |                                     | V <sub>SS</sub>       | ١    | V <sub>AREF</sub> | v    |

| Analog Supply current          | I <sub>REF</sub>  | $\checkmark$                        | —                     | 0.5  | 1.0               | mA   |

| Nonlinearity Error             |                   |                                     | —                     | -    | ± 1               |      |

| Zero Point Error               | $\langle \rangle$ | $V_{DD} = 5.0 V, V_{SS} = 0.0 V$    | _                     | -    | ± 1               | LSB  |

| Full Scale Error               |                   | V <sub>AREF</sub> = 5.000 V         | _                     | _    | ± 1               |      |

| Total Error                    |                   | V <sub>ASS</sub> = 0.000 V          | _                     | _    | ± 2               |      |

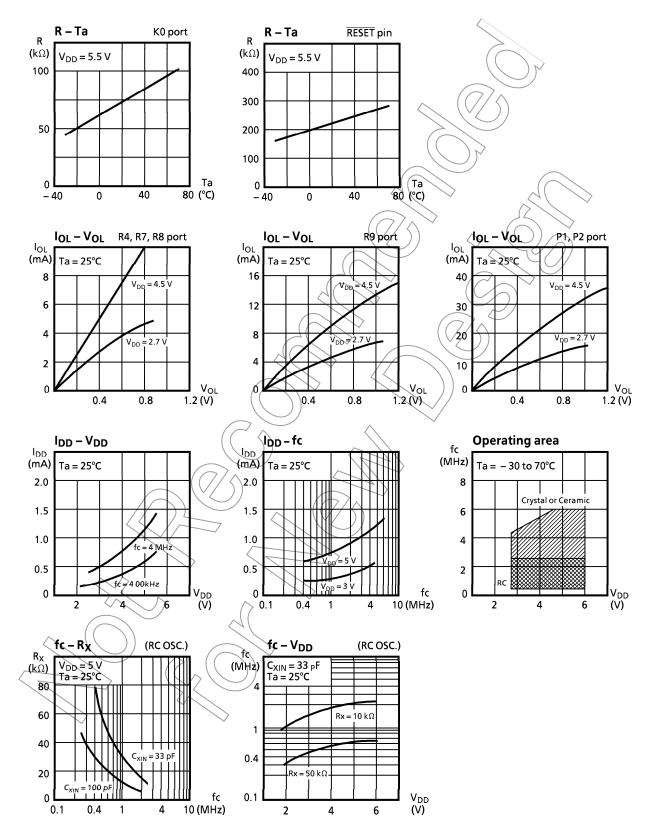

# **Typical Characteristics**